CHAPTER NO. 1 : GENESIS OF THE MARKET

1.1 Market Prelude – Introduction & Scope

1.2 The Big Picture – Objectives & Vision

1.3 Strategic Edge – Unique Value Proposition

1.4 Stakeholder Compass – Key Beneficiaries

CHAPTER NO. 2 : EXECUTIVE LENS

2.1 Pulse of the Industry – Market Snapshot

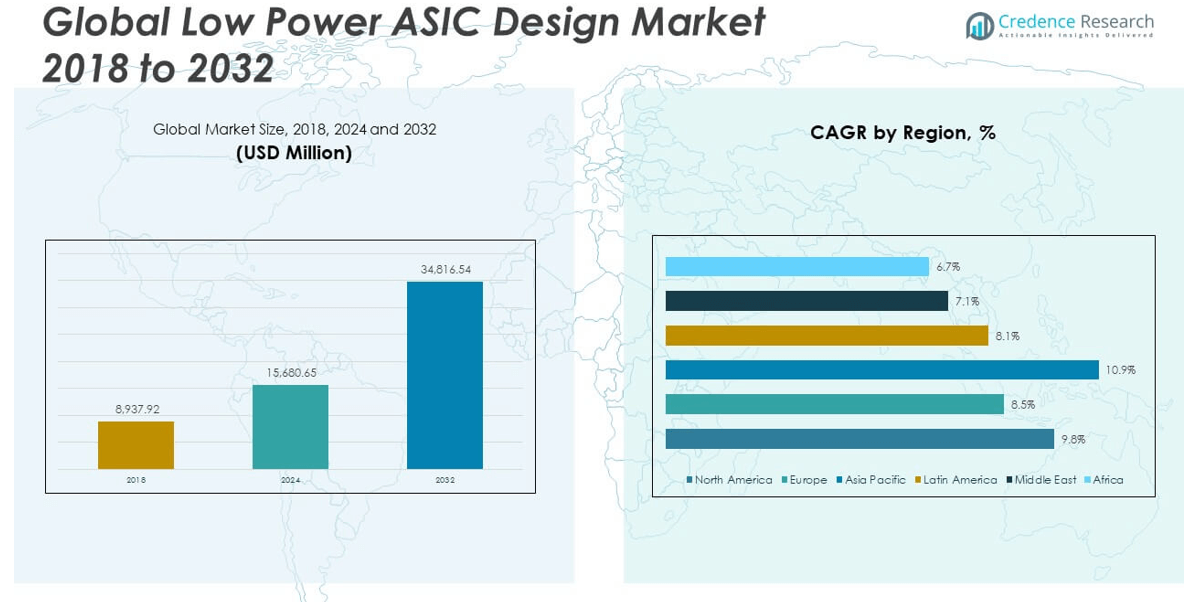

2.2 Growth Arc – Revenue Projections (USD Million)

2.3. Premium Insights – Based on Primary Interviews

CHAPTER NO. 3 : LOW POWER ASIC DESIGN MARKET FORCES & INDUSTRY PULSE

3.1 Foundations of Change – Market Overview

3.2 Catalysts of Expansion – Key Market Drivers

3.2.1 Momentum Boosters – Growth Triggers

3.2.2 Innovation Fuel – Disruptive Technologies

3.3 Headwinds & Crosswinds – Market Restraints

3.3.1 Regulatory Tides – Compliance Challenges

3.3.2 Economic Frictions – Inflationary Pressures

3.4 Untapped Horizons – Growth Potential & Opportunities

3.5 Strategic Navigation – Industry Frameworks

3.5.1 Market Equilibrium – Porter’s Five Forces

3.5.2 Ecosystem Dynamics – Value Chain Analysis

3.5.3 Macro Forces – PESTEL Breakdown

3.6 Price Trend Analysis

3.6.1 Regional Price Trend

3.6.2 Price Trend by Product

CHAPTER NO. 4 : KEY INVESTMENT EPICENTER

4.1 Regional Goldmines – High-Growth Geographies

4.2 Product Frontiers – Lucrative Product Categories

4.3 Application Sweet Spots – Emerging Demand Segments

CHAPTER NO. 5: REVENUE TRAJECTORY & WEALTH MAPPING

5.1 Momentum Metrics – Forecast & Growth Curves

5.2 Regional Revenue Footprint – Market Share Insights

5.3 Segmental Wealth Flow – Product Type & Design Type Revenue

CHAPTER NO. 6 : TRADE & COMMERCE ANALYSIS

6.1. Import Analysis by Region

6.1.1. Global Low Power ASIC Design Market Import Volume By Region

6.2. Export Analysis by Region

6.2.1. Global Low Power ASIC Design Market Export Volume By Region

CHAPTER NO. 7 : COMPETITION ANALYSIS

7.1. Company Market Share Analysis

7.1.1. Global Low Power ASIC Design Market: Company Market Share

7.1. Global Low Power ASIC Design Market Company Volume Market Share

7.2. Global Low Power ASIC Design Market Company Revenue Market Share

7.3. Strategic Developments

7.3.1. Acquisitions & Mergers

7.3.2. New Product Launch

7.3.3. Regional Expansion

7.4. Competitive Dashboard

7.5. Company Assessment Metrics, 2024

CHAPTER NO. 8 : LOW POWER ASIC DESIGN MARKET – BY PRODUCT TYPE SEGMENT ANALYSIS

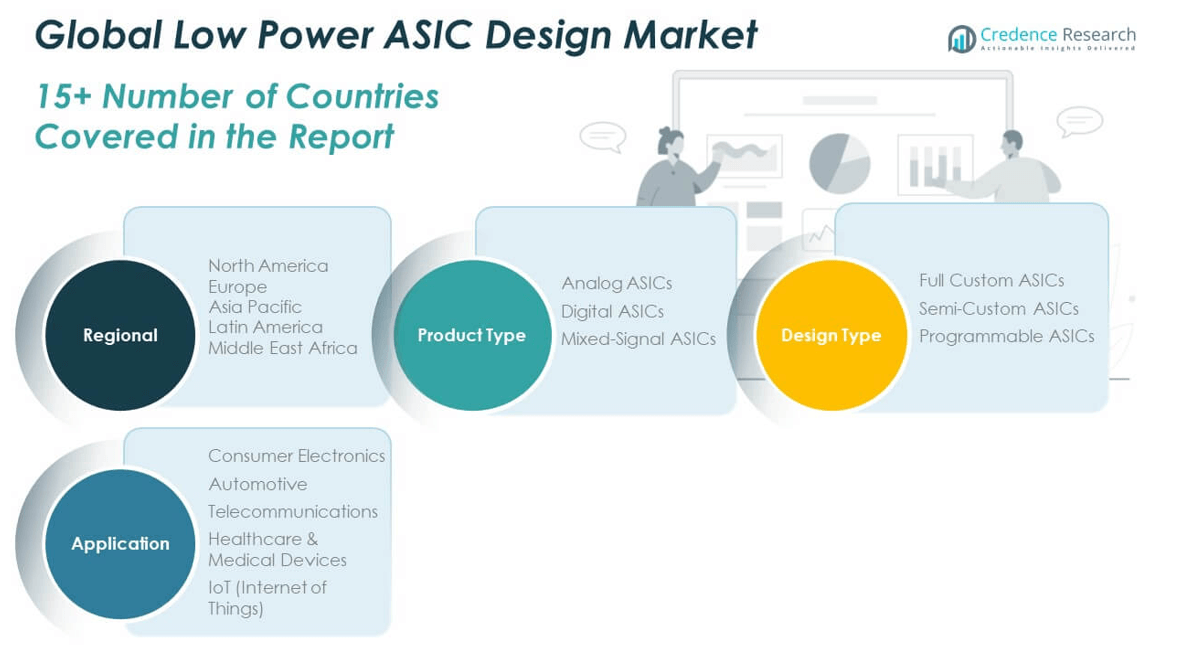

8.1. Low Power ASIC Design Market Overview by Product Type Segment

8.1.1. Low Power ASIC Design Market Volume Share By Product Type

8.1.2. Low Power ASIC Design Market Revenue Share By Product Type

8.2. Analog ASICs

8.3. Digital ASICs

8.4. Mixed-Signal ASICs

CHAPTER NO. 9 : LOW POWER ASIC DESIGN MARKET – BY DESIGN TYPE SEGMENT ANALYSIS

9.1. Low Power ASIC Design Market Overview by Design Type Segment

9.1.1. Low Power ASIC Design Market Volume Share By Design Type

9.1.2. Low Power ASIC Design Market Revenue Share By Design Type

9.2. Full Custom ASICs

9.3. Semi-Custom ASICs

9.4. Programmable ASICs

CHAPTER NO. 10 : LOW POWER ASIC DESIGN MARKET – BY APPLICATION SEGMENT ANALYSIS

10.1. Low Power ASIC Design Market Overview by Application Segment

10.1.1. Low Power ASIC Design Market Volume Share By Application

10.1.2. Low Power ASIC Design Market Revenue Share By Application

10.2. Consumer Electronics

10.3. Automotive

10.4. Telecommunications

10.5. Healthcare & Medical Devices

10.6. Biotechnology

10.7. IoT (Internet of Things)

CHAPTER NO. 11 : LOW POWER ASIC DESIGN MARKET – REGIONAL ANALYSIS

11.1. Low Power ASIC Design Market Overview by Region Segment

11.1.1. Global Low Power ASIC Design Market Volume Share By Region

11.1.2. Global Low Power ASIC Design Market Revenue Share By Region

11.1.3. Regions

11.1.4. Global Low Power ASIC Design Market Volume By Region

11.1.5. Global Low Power ASIC Design Market Revenue By Region

11.1.6. Product Type

11.1.7. Global Low Power ASIC Design Market Volume By Product Type

11.1.8. Global Low Power ASIC Design Market Revenue By Product Type

11.1.9. Design Type

11.1.10. Global Low Power ASIC Design Market Volume By Design Type

11.1.11. Global Low Power ASIC Design Market Revenue By Design Type

11.1.12. Application

11.1.13. Global Low Power ASIC Design Market Volume By Application

11.1.14. Global Low Power ASIC Design Market Revenue By Application

CHAPTER NO. 12 : NORTH AMERICA LOW POWER ASIC DESIGN MARKET – COUNTRY ANALYSIS

12.1. North America Low Power ASIC Design Market Overview by Country Segment

12.1.1. North America Low Power ASIC Design Market Volume Share By Region

12.1.2. North America Low Power ASIC Design Market Revenue Share By Region

12.2. North America

12.2.1. North America Low Power ASIC Design Market Volume By Country

12.2.2. North America Low Power ASIC Design Market Revenue By Country

12.2.3. Product Type

12.2.4. North America Low Power ASIC Design Market Volume By Product Type

12.2.5. North America Low Power ASIC Design Market Revenue By Product Type

12.2.6. Design Type

12.2.7. North America Low Power ASIC Design Market Volume By Design Type

12.2.8. North America Low Power ASIC Design Market Revenue By Design Type

12.2.9. Application

12.2.10. North America Low Power ASIC Design Market Volume By Application

12.2.11. North America Low Power ASIC Design Market Revenue By Application

12.3. U.S.

12.4. Canada

12.5. Mexico

CHAPTER NO. 13 : EUROPE LOW POWER ASIC DESIGN MARKET – COUNTRY ANALYSIS

13.1. Europe Low Power ASIC Design Market Overview by Country Segment

13.1.1. Europe Low Power ASIC Design Market Volume Share By Region

13.1.2. Europe Low Power ASIC Design Market Revenue Share By Region

13.2. Europe

13.2.1. Europe Low Power ASIC Design Market Volume By Country

13.2.2. Europe Low Power ASIC Design Market Revenue By Country

13.2.3. Product Type

13.2.4. Europe Low Power ASIC Design Market Volume By Product Type

13.2.5. Europe Low Power ASIC Design Market Revenue By Product Type

13.2.6. Design Type

13.2.7. Europe Low Power ASIC Design Market Volume By Design Type

13.2.8. Europe Low Power ASIC Design Market Revenue By Design Type

13.2.9. Application

13.2.10. Europe Low Power ASIC Design Market Volume By Application

13.2.11. Europe Low Power ASIC Design Market Revenue By Application

13.3. UK

13.4. France

13.5. Germany

13.6. Italy

13.7. Spain

13.8. Russia

13.9. Rest of Europe

CHAPTER NO. 14 : ASIA PACIFIC LOW POWER ASIC DESIGN MARKET – COUNTRY ANALYSIS

14.1. Asia Pacific Low Power ASIC Design Market Overview by Country Segment

14.1.1. Asia Pacific Low Power ASIC Design Market Volume Share By Region

14.1.2. Asia Pacific Low Power ASIC Design Market Revenue Share By Region

14.2. Asia Pacific

14.2.1. Asia Pacific Low Power ASIC Design Market Volume By Country

14.2.2. Asia Pacific Low Power ASIC Design Market Revenue By Country

14.2.3. Product Type

14.2.4. Asia Pacific Low Power ASIC Design Market Volume By Product Type

14.2.5. Asia Pacific Low Power ASIC Design Market Revenue By Product Type

14.2.6. Design Type

14.2.7. Asia Pacific Low Power ASIC Design Market Volume By Design Type

14.2.8. Asia Pacific Low Power ASIC Design Market Revenue By Design Type

14.2.9. Application

14.2.10. Asia Pacific Low Power ASIC Design Market Volume By Application

14.2.11. Asia Pacific Low Power ASIC Design Market Revenue By Application

14.3. China

14.4. Japan

14.5. South Korea

14.6. India

14.7. Australia

14.8. Southeast Asia

14.9. Rest of Asia Pacific

CHAPTER NO. 15 : LATIN AMERICA LOW POWER ASIC DESIGN MARKET – COUNTRY ANALYSIS

15.1. Latin America Low Power ASIC Design Market Overview by Country Segment

15.1.1. Latin America Low Power ASIC Design Market Volume Share By Region

15.1.2. Latin America Low Power ASIC Design Market Revenue Share By Region

15.2. Latin America

15.2.1. Latin America Low Power ASIC Design Market Volume By Country

15.2.2. Latin America Low Power ASIC Design Market Revenue By Country

15.2.3. Product Type

15.2.4. Latin America Low Power ASIC Design Market Volume By Product Type

15.2.5. Latin America Low Power ASIC Design Market Revenue By Product Type

15.2.6. Design Type

15.2.7. Latin America Low Power ASIC Design Market Volume By Design Type

15.2.8. Latin America Low Power ASIC Design Market Revenue By Design Type

15.2.9. Application

15.2.10. Latin America Low Power ASIC Design Market Volume By Application

15.2.11. Latin America Low Power ASIC Design Market Revenue By Application

15.3. Brazil

15.4. Argentina

15.5. Rest of Latin America

CHAPTER NO. 16 : MIDDLE EAST LOW POWER ASIC DESIGN MARKET – COUNTRY ANALYSIS

16.1. Middle East Low Power ASIC Design Market Overview by Country Segment

16.1.1. Middle East Low Power ASIC Design Market Volume Share By Region

16.1.2. Middle East Low Power ASIC Design Market Revenue Share By Region

16.2. Middle East

16.2.1. Middle East Low Power ASIC Design Market Volume By Country

16.2.2. Middle East Low Power ASIC Design Market Revenue By Country

16.2.3. Product Type

16.2.4. Middle East Low Power ASIC Design Market Volume By Product Type

16.2.5. Middle East Low Power ASIC Design Market Revenue By Product Type

16.2.6. Design Type

16.2.7. Middle East Low Power ASIC Design Market Volume By Design Type

16.2.8. Middle East Low Power ASIC Design Market Revenue By Design Type

16.2.9. Application

16.2.10. Middle East Low Power ASIC Design Market Volume By Application

16.2.11. Middle East Low Power ASIC Design Market Revenue By Application

16.3. GCC Countries

16.4. Israel

16.5. Turkey

16.6. Rest of Middle East

CHAPTER NO. 17 : AFRICA LOW POWER ASIC DESIGN MARKET – COUNTRY ANALYSIS

17.1. Africa Low Power ASIC Design Market Overview by Country Segment

17.1.1. Africa Low Power ASIC Design Market Volume Share By Region

17.1.2. Africa Low Power ASIC Design Market Revenue Share By Region

17.2. Africa

17.2.1. Africa Low Power ASIC Design Market Volume By Country

17.2.2. Africa Low Power ASIC Design Market Revenue By Country

17.2.3. Product Type

17.2.4. Africa Low Power ASIC Design Market Volume By Product Type

17.2.5. Africa Low Power ASIC Design Market Revenue By Product Type

17.2.6. Design Type

17.2.7. Africa Low Power ASIC Design Market Volume By Design Type

17.2.8. Africa Low Power ASIC Design Market Revenue By Design Type

17.2.9. Application

17.2.10. Africa Low Power ASIC Design Market Volume By Application

17.2.11. Africa Low Power ASIC Design Market Revenue By Application

17.3. South Africa

17.4. Egypt

17.5. Rest of Africa

CHAPTER NO. 18 : COMPANY PROFILES

18.1. TSMC (Taiwan Semiconductor Manufacturing Company)

18.1.1. Company Overview

18.1.2. Product Portfolio

18.1.3. Financial Overview

18.1.4. Recent Developments

18.1.5. Growth Strategy

18.1.6. SWOT Analysis

18.2. Intel Corporation

18.3. Qualcomm Incorporated

18.4. NVIDIA Corporation

18.5. Broadcom Inc.

18.6. Advanced Micro Devices (AMD)

18.7. Analog Devices Inc.

18.8. MediaTek Inc.

18.9. STMicroelectronics

18.10. Xilinx